Integrating High Accuracy Timing IP Core (HATI) on Xilinx FPGAs

## HATI IP Core High Accuracy Timing IP

The HATI (High Accuracy Timing IP) is a FPGA core designed to provide sub-nanosecond synchronization accuracy by using 1 Gbps optical fiber links. The core is based on precise internal clock corrections to achieve sub-nanosecond synchronization accuracy. Its architecture allows to adapt the IP to different platforms. These are some of its major features:

- Sub-nanosecond time accuracy.

- Distance range: over 80 km using fiber without amplifiers and calibration.

- Dynamic compensation of asymmetries caused by weather conditions.

- Minimal data bandwidth consumption.

- Easily integrable.

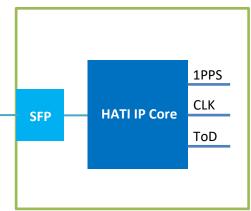

The HATI IP Core contains the whole design from the transceiver to an embedded ARM that executes a Linux OS, including the mandatory clocking circuitry to achieve a highly accurate synchronization.

info@sevensols.com support@sevensols.com (+34) 958 285 024 C/ Periodista Rafael Gómez Montero, 2 Oficina 13 - Edf. CETIC 18014 Granada, SPAIN.

Solutions

## **Specifications / HATI IP Core**

Currently, the HATI IP Core is **only available on Xilinx Zynq** programmable SoCs because of its internal vendor dependent architecture. The example design is developed for a Xilinx Virtex-7 FPGA VC709 Connectivity Kit, but it can be adapted to work on different platforms.

Its purpose is to work as a last hop timing connecting to the optical interfaces of a WR Z16 device. The developed technology allows to correct the internal clock offset after receiving periodical data exchanges from the master WR Z16.

This design is a technology demonstrator that shows the capability to **integrate a high accurate timing system on many FPGA** based boards. For this reason, it has a modular architecture that allows the IP to coexist in different scenarios. Future integration projects can be discussed for different platforms, use cases and vendors.

The resource utilization on the Virtex-7 VC709 development kit is shown at **Table 1**.

| LUT    | 5719  | 433200 | 1,32  |

|--------|-------|--------|-------|

| LUTRAM | 48    | 174200 | 0,03  |

| FF     | 5948  | 866400 | 0,69  |

| BRAM   | 39,50 | 1470   | 2,69  |

| DSP    | 3     | 3600   | 0,08  |

| 10     | 20    | 850    | 2,35  |

| GT     | 1     | 36     | 2,78  |

| BUFG   | 5     | 32     | 15,63 |

|        |       |        |       |

Table 1: HATI utilization on the Virtex-7 VC709 kit.

WR Z16

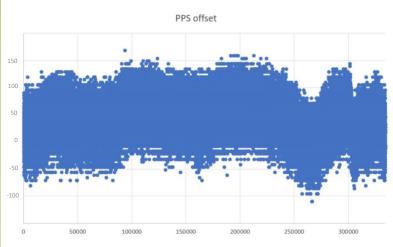

The accuracy level is measured by comparing the 1PPS (Pulse Per Second) outputs from a master WR Z16 device and a VC709 board that integrates the HATI core configured as a slave. It is a long-term measurement using a short fiber. The obtained peak-to-peak time offset is **lower than 300 picoseconds.**

Figure 1: Long-term PPS offset measurement.

| Max-Min (ps)   | 280,66      |  |

|----------------|-------------|--|

| Mean (ps)      | 52,54       |  |

| Dev. Std. (ps) | 43,15952618 |  |

Table 2: Long-term PPS offset measurement results.

Xilinx Virtex-7 VC709 evaluation kit